TSMC, le principal fondeur de puces au monde, souhaite entamer la production de puces selon le processus de 2 nanomètres en 2025. La firme utilisera aussi la technologie des nanosheets pour de meilleures performances.

La technique, qualifiée de N2 par TSMC, promet un gain de vitesse jusqu’à 15 pour cent et une consommation d’énergie inférieure de 25 à 30 pour cent en fonction de la configuration. N2 permettrait d’accueillir en outre jusqu’à dix pour cent de transistors en plus par rapport à la précédente technique N3E.

Pour la production, TSMC passera de la technique finfets à une architecture nanosheets. Voilà qui devrait également générer de meilleures performances et une réduction de la consommation d’énergie. Il y a un an, IBM fut le premier à présenter la technologie de la puce de 2 nanomètres, mais à l’époque, il s’agissait d’une production dans un laboratoire de test. La production à grande échelle représente un défi nettement plus important.

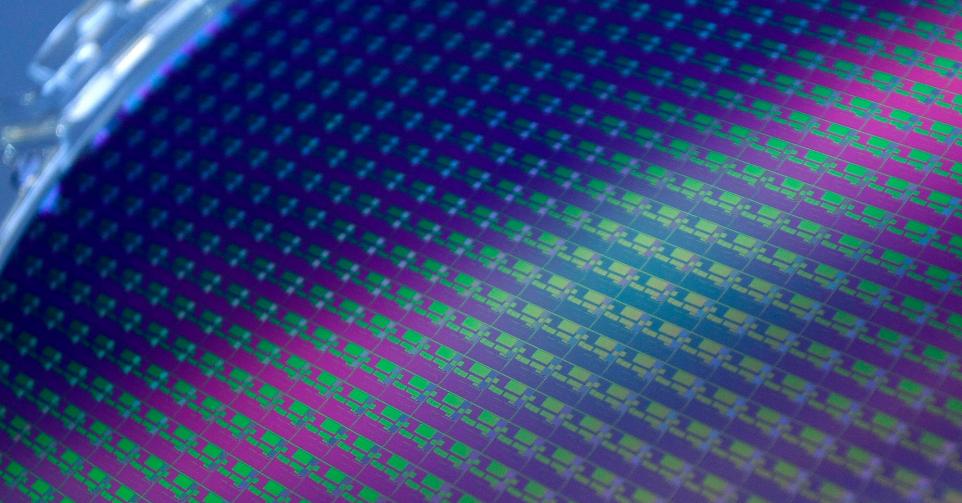

La technologie des puces voit se réduire le processus de production à chaque génération. Il en résulte que les transistors peuvent être toujours davantage rapprochés et nécessitent donc moins de courant pour fonctionner. Actuellement, les puces M1 et M2 d’Apple par exemple sont fabriquées selon un processus de 5 nanomètres. La prochaine génération sera de l’ordre de 3 nanomètres, avant de passer à 2 nanomètres.