Le secteur des puces électroniques est confronté à des attentes et à des défis majeurs. Pour répondre aux exigences de l’IA, les puces doivent non seulement devenir plus flexibles, mais aussi s’étendre (littéralement) dans plusieurs dimensions pour obéir à la loi de Moore. Un défi de taille, mais pas impossible, selon Luc Van den Hove, directeur de l’imec.

L’institut louvaniste de recherche sur les puces électroniques imec organise cette semaine sa grande conférence à Anvers. ITF World est loin d’être un événement belge. Parmi les intervenants figurent notamment des représentants de Google Deepmind, Nvidia et Apple, qui expliquent avec enthousiasme comment ils envisagent les révolutions technologiques dans leur domaine. On y entend souvent cependant que l’innovation résulte d’une collaboration avec l’imec.

Mais tous ces progrès débutent par la puce en tant que source de la puissance de calcul. Pendant des années, le secteur a pu continuer à fabriquer des transistors toujours plus petits, permettant d’en placer davantage sur une seule puce. Plus petit signifie généralement aussi plus économe en énergie. Mais réduire toujours plus la taille de ces transistors devient physiquement plus compliqué. Parallèlement, la demande de puissance de calcul se fait plus grande que jamais en raison de l’IA.

‘Avec l’arrivée de DeepSeek, on a pensé pendant un certain temps que la demande de puissance de calcul allait diminuer. Tel n’est pas le cas, car il en résultera en fait une adoption plus rapide de l’IA et cela nécessitera donc beaucoup plus de puissance de calcul’, déclare Van den Hove dans son discours d’ouverture à ITF World.

Le directeur de l’imec affirme que nous n’en sommes encore qu’aux débuts en soulignant qu’il existe désormais différents types d’IA amenés à collaborer à terme: ‘La prochaine génération d’IA sera plus hétérogène. Nous avons l’IA générative, l’IA agentique, l’IA physique, qui peuvent interagir avec le monde dans des domaines comme la santé ou l’automobile. Mais nous allons combiner plusieurs modèles interagissant entre eux de manière intuitive. Cela ne fera qu’accroître la demande de puissance de calcul.’

Deux vitesses

Cette demande croissante nous obligera à développer des puces et des algorithmes nécessitant moins d’énergie. Van den Hove évoque cependant un obstacle:

‘Nous sommes passés des CPU aux GPU et aux implémentations ASIC où les algorithmes sont intégrés aux puces pour consommer moins d’énergie. Mais les modèles d’IA évoluent plus rapidement que la vitesse de développement d’une telle puce. Au moment où on intègre un algorithme dans une puce, il en existe déjà de meilleurs. Il y a un problème de synchronisation qu’il faut résoudre. C’est pourquoi nous aurons besoin d’une architecture informatique plus flexible et reconfigurable dans des plateformes technologiques polyvalentes.’

Chez Nvidia, on ressent également la nécessité d’aborder le secteur différemment. Vivek Singh, Vicepresident Advanced Technology de l’entreprise, évoque aussi l’augmentation massive du nombre de transistors par puce et la façon dont ces puces peuvent exécuter des calculs plus complexes à chaque génération, mais cela ne suffit encore et toujours pas à répondre à la demande.

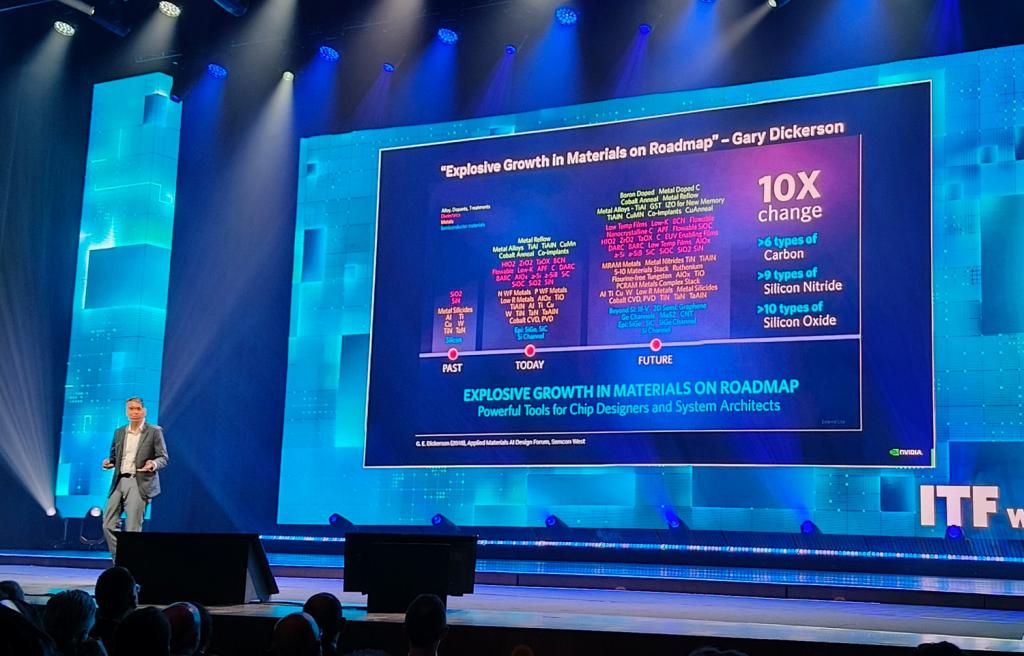

Cela signifie que les centres de données d’IA nécessitent beaucoup plus de puissance qu’un centre de données traditionnel. Parallèlement, les puces deviennent aussi plus complexes physiquement. Dans le passé, une puce intégrait l’une ou l’autre matière première, alors qu’aujourd’hui il y en a plusieurs dizaines. A l’avenir, une centaine au moins de différents types de métaux, de semi-conducteurs et de substances seront nécessaires pour les traitements.

‘Il faut un changement fondamental. Nous aurons besoin de centaines de centres de données supplémentaires pour répondre à la demande. Une paire de 15 mégawatts, c’est encore gérable. Mais des centaines de centres de données qui nécessitent des gigawatts, le monde et le climat ne pourront y faire face’, explique Singh.

Evolutions en 2D et 3D

Le mouvement en cours depuis des décennies vers des transistors plus nombreux et plus petits sur une seule et même puce se heurte également à des limites physiques. Van den Hove se réfère ici à l’étroite collaboration avec le fabricant néerlandais de machines à puces ASML pour rendre possible cette évolution en 2D.

La mise à l’échelle s’étend également vers le haut, dans des piles 3D, également appelées advanced packaging. ‘On empile les transistors les uns sur les autres et on obtient ainsi un effet d’échelle supplémentaire en plus du lithography based scaling (où on installe davantage de transistors plus petits sur une même puce, ndlr).’

Cette méthode est débattue depuis plusieurs années, mais à ITF World, il est clair que cela devient l’approche pour demain, et que les principaux acteurs regardent dans cette direction. Scott DeBoer, Chief Technology & Product Officer chez Micron, qui se concentre surtout sur la mémoire et le stockage, envisage un rôle-clé pour l’advanced packaging en support de la révolution de l’IA.

Dans son domaine également, des recherches sont menées sur la manière dont le développement de la (puce) mémoire peut faire de nouveaux progrès pour répondre à la forte demande de l’IA, de préférence dans du matériel qui ne nécessite pas encore davantage d’énergie ou ne génère pas de chaleur. Il est question de résoudre des énigmes technologiques, alors que les composants individuels sont encore en cours de développement.

Couches spécialisées

Van den Hove est enthousiaste quant à la manière dont l’empilement des couches de puces engendrera de nouvelles choses: ‘Chaque couche pourra avoir sa propre spécialité et conduire à des processus optimisés et simplifiés qui, à leur tour, permettront une mise à l’échelle supplémentaire, ce que nous appelons CMOS 2.0.’

Van den Hove compare CMOS 2.0 à un FPGA sous stéroïde. Les FPGA sont des circuits intégrés hautement programmables et donc facilement adaptables à l’objectif final. Mais les transistors 3D (CFET ou complementary field-effect transistor), conjointement à l’advanced packaging, joueront également un rôle pour créer un nouveau type de puce nettement plus performante.

‘La façon dont nos puces sont conçues, va radicalement changer. Dans un environnement 2D, tout a une place. En 3D, on peut envisager tout un ensemble de supercellules standardisées, avec mémoires L1 et L2, network on a chip, functional grains, registers, mais aussi un réseau de contrôle reconfigurable. C’est ce dernier qui sera la clé de l’adaptabilité.

Pour l’imec, il n’existe pas de solution unique pour rendre les puces exponentiellement plus performantes. C’est une histoire ‘et-et-et’. L’architecture, les développements de l’IA, les matériaux,…, mais aussi de nouveaux concepts comme les super semi-conducteurs ou l’informatique quantique peuvent mener au progrès.

‘Les défis sont énormes, mais c’est une période passionnante pour le secteur‘, conclut le directeur de l’imec.