Le magazine Science décrit une nouvelle puce ‘cérébrale’, le résultat d’une collaboration entre IBM, Cornell et IniLabs, comme base d’ordinateurs ‘non-von Neumann’.

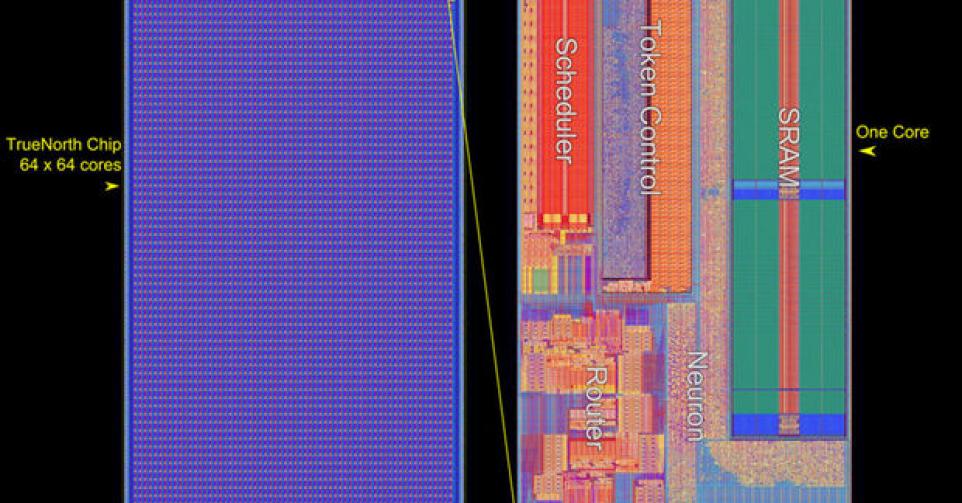

Avec 4,5 milliards de transistors, cette toute nouvelle puce – ‘TrueNorth’ dans le programme de recherche SyNapse (Systems of Neuromorphic Adaptive Plastic Scalable, financé entre autres par le département américain de recherche militaire DARPA) – est aussi la plus volumineuse qu’IBM ait jamais construite. Les transistors sont répartis sur notamment un réseau d’1 million de ‘neurones’ (4.096 blocs de 250 neurones) et de 256 millions de ‘synapses’ (connexions entre neurones). Voilà qui indique aussitôt que cette puce dispose d’une structure ressemblant à celle du cerveau (d’un mammifère). Son fonctionnement est aussi massivement parallèle de nature et diffère ainsi fondamentalement de l’actuelle ‘approche von Neuman’ sérielle dans les processeurs. Les ‘neurones’ et ‘synapses’ combinent les fonctions de mémoire et de traitement et communiquent entre eux au moyen de ‘spikes’.

L’architecture du processeur ‘TrueNorth’ avait été simulée fin 2012 déjà dans le cadre du projet ‘Compass’, sur le superordinateur IBM Blue/Q installé dans le laboratoire de recherche Livermore Lawrence.

Réseaux neuraux et superordinateurs

Le processeur serait capable d’effectuer 46 milliards d’opérations synaptiques à la seconde et ne consommerait que très peu de courant (quelque 70 milliwatts au maximum contre quelque 35 à 145 milliwatts pour les processeurs classiques). Une application test en matière de reconnaissance vidéo dans le trafic (400×240 pixels d’entrée vidéo à 30fps) n’a ainsi consommé que 63 milliwatts. Une même application sur un notebook classique a comparativement tourné 100 fois plus lentement et a consommé 100.000 fois plus de courant.

Les chercheurs considèrent cette architecture comme répondant particulièrement bien aux “applications utilisant des réseaux neuraux complexes en temps réel, comme la détection et la classification multi-objet”. L’on peut penser ici à des applications en matière de traitement de l’image, du son et du signal (tels que provenant de réseaux distribués de capteurs, y compris des informations issues d’avions sans pilote (militaires) et d’autres véhicules). En combinant plusieurs de ces puces SyNapse, l’on envisagerait de créer des systèmes ayant la puissance d’un superordinateur pour des applications exigeant aujourd’hui la puissance (et la consommation de courant) de vastes grappes (clusters) de puissantes machines.

Le principal défi à relever sera assurément la nouvelle approche requise du développement software. Plus tôt cette année, IBM avait du reste annoncé un modèle de programmation ‘corelet’ adapté et va aussi prévoir une bibliothèque de fragments de code prêts à l’emploi.

Il est de plus intéressant de noter que de nouvelles architecture ‘non-von Neumann’ ont récemment assez souvent été présentées, comme ‘The Machine’ de HP plus tôt cette année encore.