Le centre de recherche imec de Louvain, en collaboration avec le fabricant de machines à puces ASML, a imprimé des modèles sur base de la lithographie High NA EUV. Cette méthode devrait être à la base des prochaines générations de puces.

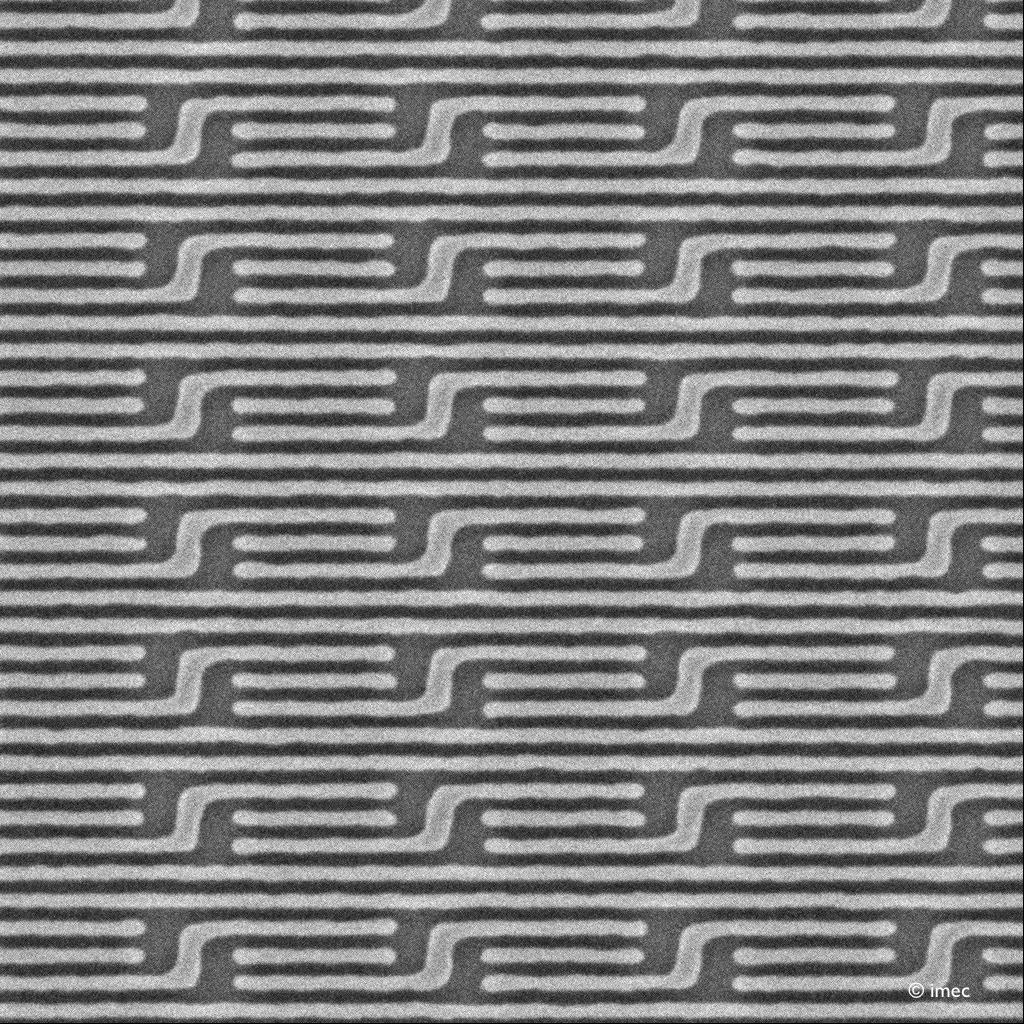

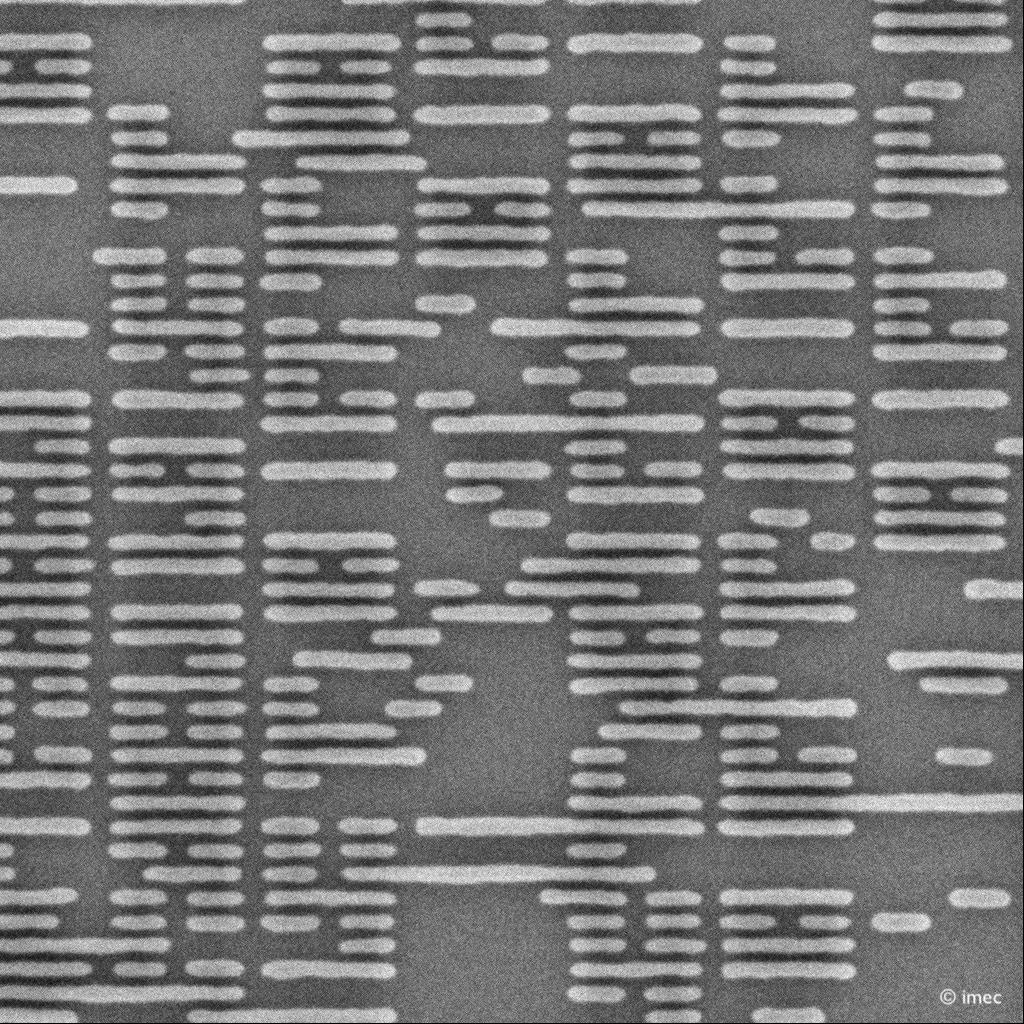

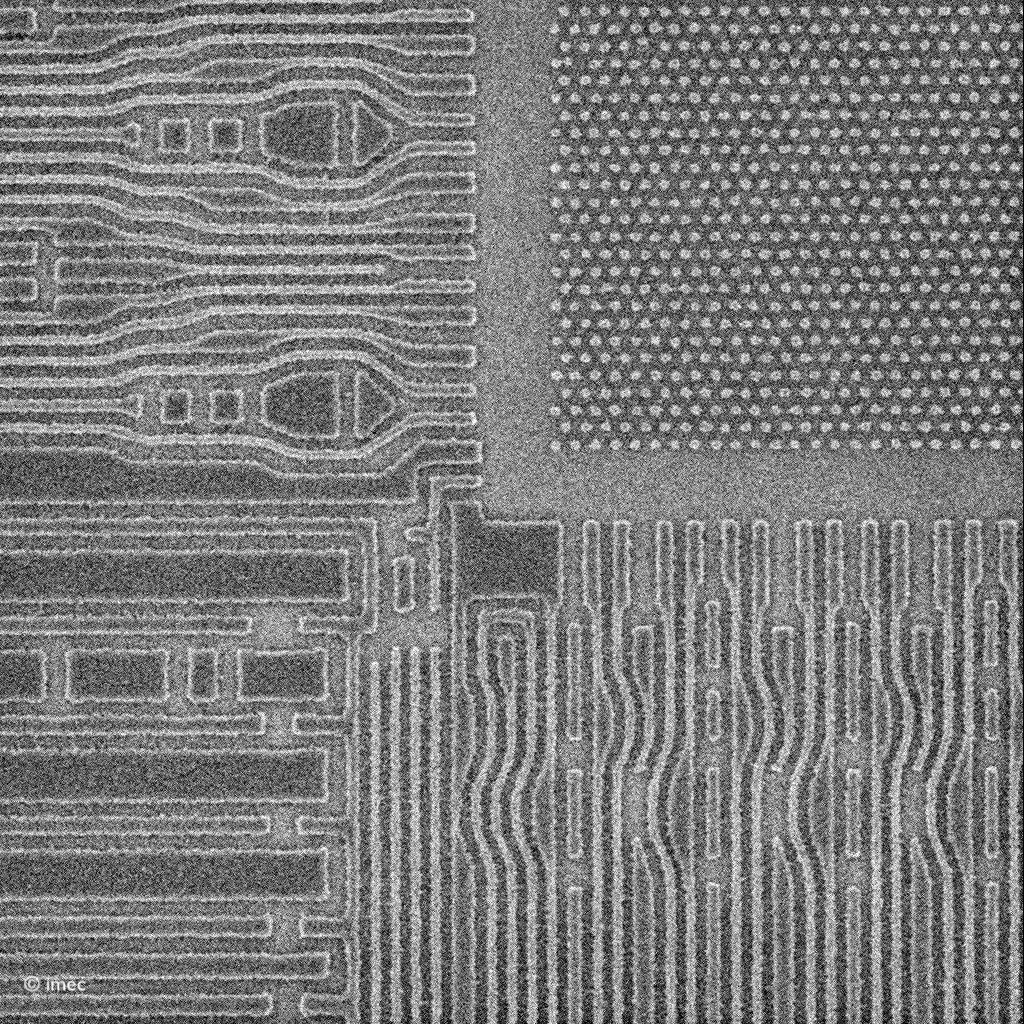

Dans un laboratoire partagé avec ASML, l’imec a appliqué des structures de modèle à 9,5 nanomètres (pitch de 19 nanomètres), des vias aléatoires avec une distance centre à centre de 30 nanomètres, des fonctionnalités 3D à pitch de 22 nanomètres et une disposition spécifique DRAM sur P32 nm et ce, en exposition unique.

C’est là un résumé très complexe signifiant que l’imec est capable d’appliquer avec succès la nouvelle méthode de lithographie High NA EUV. Cette dernière représente la prochaine étape dans le traitement de fragments de silicium ‘vides’ pour en fabriquer des puces.

Pour expliquer ce que signifie exactement High NA EUV, il faut savoir que les puces sophistiquées modernes sont fabriquées en y projetant une lumière ultraviolette extrême (EUV). NA signifie ‘numerical aperture’, à savoir l’angle d’ouverture permettant de rendre l’image plus nette et les lignes exposées plus petites.

Exposition unique

La technologie permet de nouveau d’installer plus de transistors (beaucoup plus petits) sur une même puce, ce qui augmente ses performances et réduit la consommation d’énergie.

Le fait que cela puisse se faire en exposant le matériau une seule fois (‘single exposure’) n’est pas sans importance, car cela limite le nombre d’étapes et donc aussi le nombre d’erreurs possibles dans la production des puces.

ASML, qui fabrique des machines de production de puces, et l’imec, qui collabore avec presque tous les fondeurs de puces en tant que site de recherche neutre, ont ouvert début juin leur laboratoire commun de lithographie High NA EUV à Veldhoven, où est établi le siège d’ASML. La méthode High NA EUV, en préparation depuis 2018, devrait entrer en production de masse vers 2025-2026.

‘Cela augmentera le rendement (la quantité de puces opérationnelles pouvant être produites simultanément, ndlr) et réduira la durée de cycle et même les émissions de CO2 par rapport aux méthodes 0.33 NA EUV multi-modèles existantes’, a déclaré Luc Van den hove, CEO de l’imec, lors de l’inauguration du laboratoire.

L’imec affirme qu’en plus des structures logiques, il a également été en mesure de fournir des concepts intégrant le ‘storage node landing pad’ intégrant la ‘bit line periphery’ pour la DRAM. Selon le chercheur en matière de puces, cela montre qu’une exposition unique peut remplacer plusieurs couches de ‘maskers’.

‘Les résultats obtenus démontrent le potentiel unique de la méthode High NA EUV pour permettre une imagerie en une seule impression de fonctionnalités 2D à scaling agressif. Ce faisant, nous améliorons la flexibilité du concept et réduisons le coût et la complexité de l’application des modèles’, déclare Steven Scheer, senior vicepresident compute technologies & systems and compute system scaling chez l’imec.